daneva australia pty ltd 66 bay road, sandringham australia, 3191 tel. (03) 598 5622

# Electrically Alterable Non-Volatile Memory Handbook

GENERAL INSTRUMENT

# ELECTRICALLY ALTERABLE NON-VOLATILE MEMORY HANDBOOK

## **DATA SHEETS**

# **APPLICATION NOTES**

## TABLE OF CONTENTS—PAGE 2 MARCH 1983

Revision A

©Copyright 1983 GENERAL INSTRUMENT CORPORATION

The information in this publication, including schematics, is suggestive only. General Instrument Corporation does not warrant, nor will it be responsible or liable for, (a) the accuracy of such information, (b) its use or (c) any infringement of patents or other rights of third parties.

## **TABLE OF CONTENTS**

# DATA SHEETS

| FUNCTION                 | DESCRIPTION                                                                                  | PART<br>NUMBER | PAGE<br>NUMBER |  |

|--------------------------|----------------------------------------------------------------------------------------------|----------------|----------------|--|

|                          | Electrically Alterable I                                                                     | Von-Volatil    | e Memory       |  |

| 82 BIT EAROM             | 82 bits organized 82 x 1                                                                     | ER0082         | 5              |  |

| 700 BIT<br>SERIAL EAROM  | 700 bits organized 50 x 14                                                                   | ER1451         | 8              |  |

| 1400 BIT<br>SERIAL EAROM | 1400 bits organized 100 x 14                                                                 | ER1400         | 11             |  |

|                          |                                                                                              | ER2051         | 14             |  |

| 512 BIT EAROM            | 512 bits organized 32 x 16                                                                   |                | 14             |  |

|                          |                                                                                              | ER2051HR       | 14             |  |

|                          |                                                                                              | ER2055         | 17             |  |

| 512 BIT EAROM            | 512 bits organized 64 x 8 ER2055IR                                                           | 17             |                |  |

|                          |                                                                                              | ER2055HR       | 17             |  |

|                          | 1K bits organized 128 x 8                                                                    | ER5901         | 21             |  |

| 1K N-CHANNEL<br>EEPROM   |                                                                                              | ER5901IR       | 21             |  |

| LLITION                  |                                                                                              | ER5901HR       | 21             |  |

|                          |                                                                                              | ER3400         | 28             |  |

| 4096 BIT EAROM           | 4096 bits organized 1024 x 4                                                                 |                | 28             |  |

|                          |                                                                                              | ER3400HR       | 28             |  |

| 8192 BIT EAROM           | 0400 hits assessment 0040 at 4                                                               | ER2810IR       | 34             |  |

| 6192 BIT EAROW           | 8192 bits organized 2048 x 4                                                                 | ER2810HR       | 34             |  |

|                          |                                                                                              | ER5716         | 38             |  |

| 16K N-CHANNEL<br>EEPROM  | 16K bits organized 2048 x 8 ER5716IR                                                         | ER5716IR       | 38             |  |

| EE! TIOM                 |                                                                                              | ER5716HR       | 38             |  |

|                          |                                                                                              | ER5816         | 42             |  |

| WORD ALTERABLE           | Electrically word alterable 16K bits organized 2048 x 8, 5V operation in read mode. ER5816IR |                |                |  |

| ION DIT EEPHOW           |                                                                                              | ER5816HR       | 42             |  |

|                          |                                                                                              | ER5916AB       | 46             |  |

| WORD ALTERABLE           | Electrically word alterable 16K bits organized 2048 x 8, 5V operation in all modes.          | ER5916IR       | 46             |  |

|                          |                                                                                              | ER5916HR       | 46             |  |

#### Non-Volatile Static RAN

4K N-CHANNEL NON-VOLATILE STATIC RAM

4K bits organized 512 x 8

ER5304 53

# APPLICATION NOTES

| BULLETIN<br>NUMBER | TITLE                                                                  | PAGE<br>NUMBER |  |  |  |

|--------------------|------------------------------------------------------------------------|----------------|--|--|--|

| 1215               | 5 EAROM — The Electrically Word Alterable Memory for Permanent Storage |                |  |  |  |

| 1223               | New EEPROM Removes Write/Erase Necessity                               | 65             |  |  |  |

| 1202A              | The Role of Non-Volatile Memories in Consumer Electronics              | 72             |  |  |  |

| 1217               | The ER3400: An Easy to Use 4K EAROM                                    | 75             |  |  |  |

| 1210               | Data Retention Testing of ER3400                                       | 79             |  |  |  |

| 1218               | Interfacing the ER3400 to an Eight Bit Microcomputer                   | 81             |  |  |  |

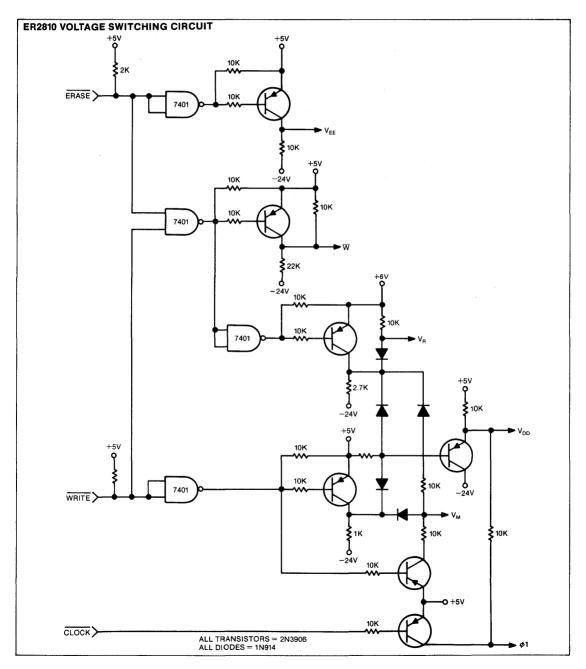

| 1219               | A Voltage Switching Circuit for the ER2810                             | 85             |  |  |  |

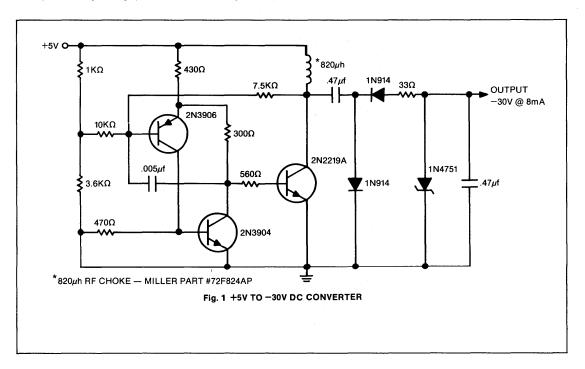

| 1220               | Generating EAROM Programming Voltages from a 5 Volt Supply             | 87             |  |  |  |

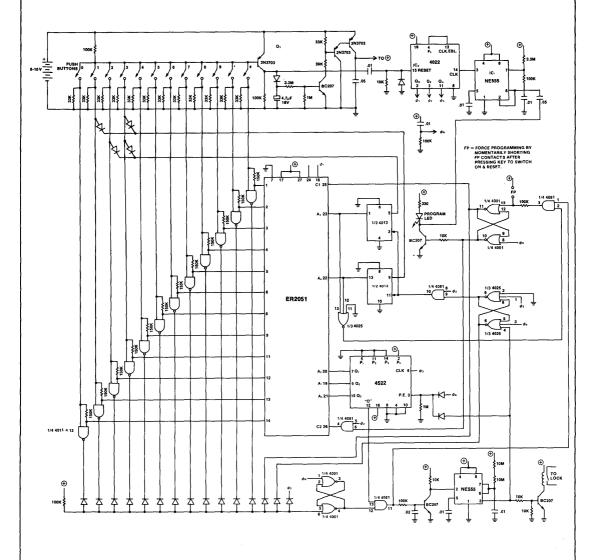

| 1206B              | Electronic Digital Lock                                                | 89             |  |  |  |

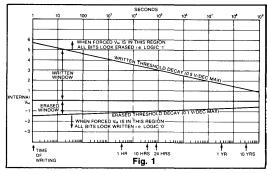

| 1214               | ER1400: Measuring Data Retention Times                                 | 92             |  |  |  |

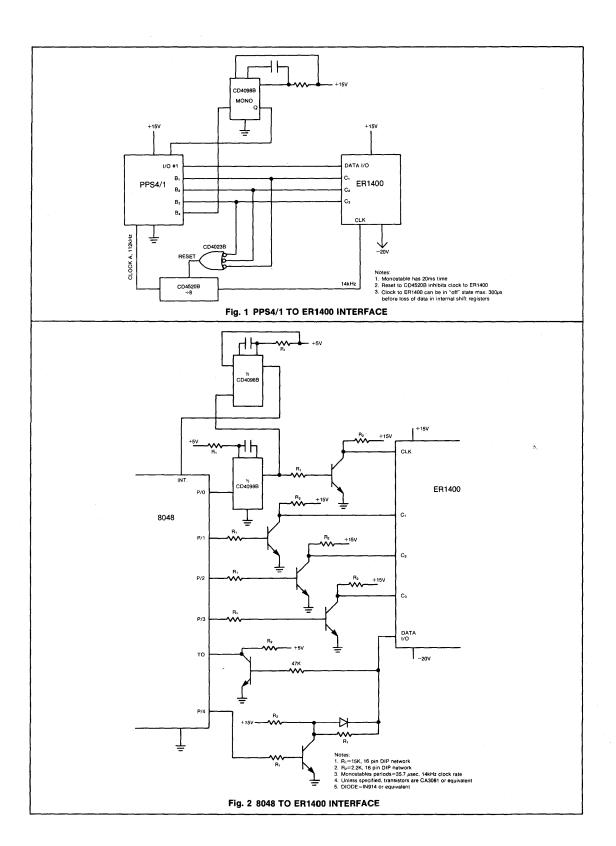

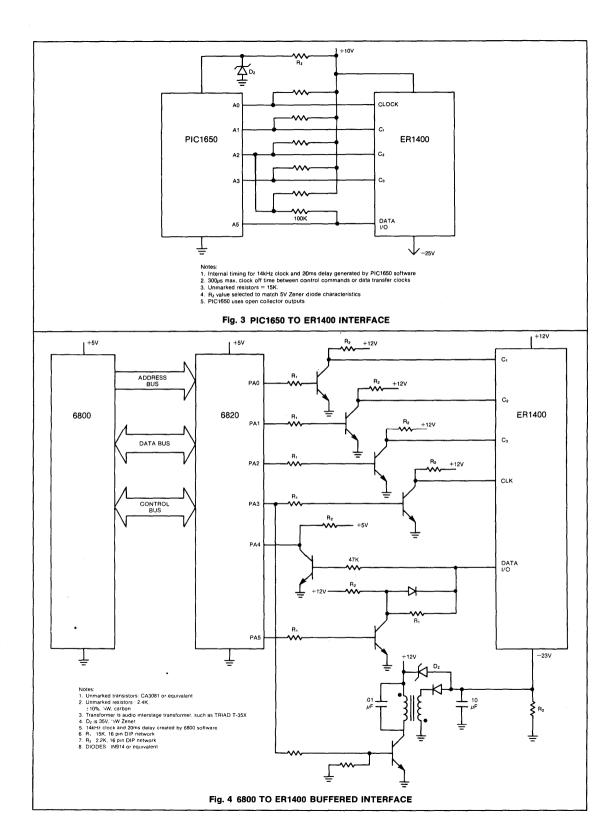

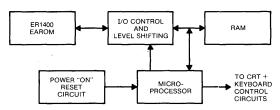

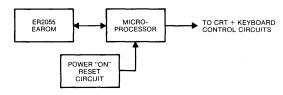

| 1207C              | Microprocessor Interfaces to the ER1400 EAROM                          | 94             |  |  |  |

| 1209B              | EAROMs Replace Mechanical Switches                                     | 99             |  |  |  |

| 1221               | 1221 ER2055 Benchtop Programmer                                        |                |  |  |  |

| 1222               | Measuring Data Retention of the ER0082                                 |                |  |  |  |

| 1224               | The ER5901: Designers Choice for Low Cost Small Memory Application     | 109            |  |  |  |

# **DATA SHEETS**

# **Electrically Alterable Non-Volatile Memory**

# **Non-Volatile Static RAM**

Note

EEPROMs and EAROMs are equivalent terms used to describe Electrically Alterable Non-Volatile Memories.

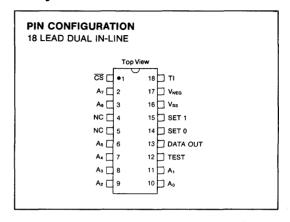

#### ER0082

#### 82 Bit Electrically Alterable Read Only Memory

#### **FEATURES**

- 82 x 1 Bit Organization

- Addressing by Two 4-bit BCD Digits

- +5V, -30V Power Supplies

- Set Inputs Have Debounce Circuits

- Bit Erasable

- 100 usec Read Access Time

- Minimum Data Retention, 7 Years Unpowered, 2 Years Powered

- P-Channel Output Transistor, Open Drain, Pull-Down Resistor

- Control, Address and Data Inputs TTL or CMOS Compatible

- Ideally Suited for T.V. Receiver Channel Selection

#### DESCRIPTION

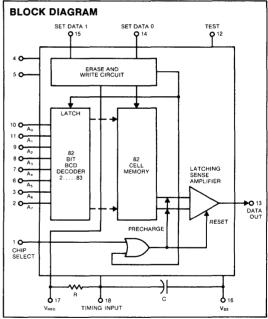

The ER0082 is a 82 x 1 bit electrically alterable read only memory. This device can be used as part of a television receiver tuner control system. The memory is programed by the user to maintain a record of channels the user wishes to be tuned, and is non-volatile in that the information stored within is not affected by the condition of or the sequencing of power supplied to the chip.

#### **OPERATION**

#### **Memory Address**

The address is provided by two positive logic binary coded decimal (BCD) digits, LSD (A<sub>0</sub>-A<sub>3</sub>) and MSD (A<sub>4</sub>-A<sub>7</sub>) (least and most significant digits); i.e. 8 bits which supply the address of a bit in the memory. There is an address in memory associated with each of the BCD numbers 2 through 83. Addresses outside the range of 2 to 83 at the LSD and MSD inputs do not cause any modification of the stored bits or change in the output data.

Example: Address 83 = 10000011 (

$$A_7...A_0$$

)

Address 2 = 00000010 ( $A_7...A_0$ )

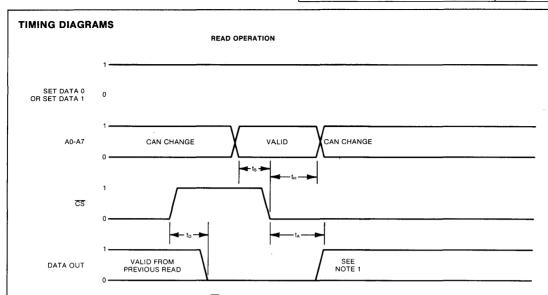

Address changes must occur only during  $\overline{CS}$  high and must be stable at least  $20\mu$ s before  $\overline{CS}$  goes low.

#### **Memory Read**

The negative transition of  $\overline{CS}$  (from a "1" level to a "0" level) initiates a memory read cycle, except when the transition occurs during a memory alteration cycle, in which case the transition is ignored. A read cycle will cause the DATA OUT pin to indicate the state of the memory bit read. The DATA OUT pin will retain the state until either  $\overline{CS}$  goes to "1" or a memory alteration cycle is initiated. DATA OUT will show the contents of the address  $100\mu s$  after  $\overline{CS}$  starts falling. When  $\overline{CS}$  is high the DATA OUT pin is low. The DATA OUT pin is internally pulled up to the positive supply,  $V_{SS}$  and for a "0" output the DATA OUT pin floats with an external pull-down ( $10K\Omega$ ) to ground.

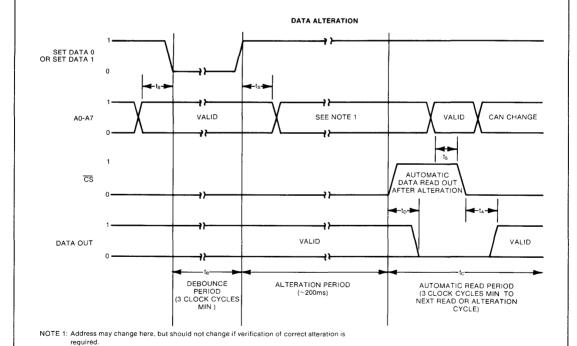

#### **Memory Alteration**

A memory alteration cycle is initiated only when the SET DATA "0" or the SET DATA "1" input, but not both, has been continuously at "0" for the specified debounce time. This allows an input to be entered via a contact closure to ground using switches. These inputs are connected to Vss via internal pull-ups. During the alteration cycle the address is held latched within the LSI. Changes in the address and SET DATA inputs are ignored, and the DATA OUT pin is held at "0". Only one memory bit may be erased or written during any single memory alteration cycle. The alteration cycle, once initiated, must go to completion. Upon

completion of an alteration cycle or the fall of  $\overline{CS}$  whichever occurs last, the memory bit corresponding to the current input address will be read and output on the DATA OUT terminal. A memory read of a bit altered due to SET DATA "0" input will cause the DATA OUT pin to be "0". Similarly, a read of a bit altered due to a SET DATA "1" input will cause the DATA OUT pin to be "1". The SET DATA inputs have internal circuits to provide delays for interfacing to mechanical switches or relays. Each successful debounce of a SET DATA input will initiate only one memory alteration cycle. Another alteration cycle will not occur until both

GENERAL INSTRUMENT

ER0082

SET DATA inputs have remained continuously at a "1" level for the specified release time and only one of the SET DATA inputs has again been successfully debounced. After an alteration cycle is complete, a read cycle may not be initiated by CS until 3 cycles of the clock on the "Timing" input pin have occurred (about 12.5ms for a nominal 200Hz frequency).

#### **Timing**

This is an input provided for external components used for a timing reference. A resistor (680K) and a capacitor (.01 $\mu$ F) may be connected to this input to provide a 200Hz nominal clock frequency. A lower capacitor or resistor value will provide a higher frequency. The timer will run only during a read cycle, alteration cycles, or while timing a debounce or release. Increasing the clock frequency will shorten these times. The frequency can vary from 50Hz min to 500Hz max. and may be measured on the timing pin.

#### **PIN FUNCTIONS**

| NAME                           | FUNCTIONS                                                                                                                                                                            |

|--------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A <sub>0</sub> -A <sub>7</sub> | Address bus used to select 1 of 82 addresses.                                                                                                                                        |

| <del>cs</del>                  | Chip select. An active low signal which enables or disables the data out pin.                                                                                                        |

| Data Out                       | DATA OUT is a single bit indicating the state of the addressed memory cell.                                                                                                          |

| Set Data 0<br>Set Data 1       | These are inputs by which the user can modify the memory contents.                                                                                                                   |

| T!                             | Provides a timing reference for internal timing cycles.                                                                                                                              |

| TEST                           | A TEST pin which provides a connection to V <sub>m</sub> , an internal voltage used for evaluating chip memory performance. In normal operation this pin should be left unconnected. |

| Vss                            | Substrate Supply. Nominally +5V.                                                                                                                                                     |

| V <sub>NEG</sub>               | Power supply input. Nominally -30V.                                                                                                                                                  |

#### **ELECTRICAL CHARACTERISTICS**

#### Maximum Ratings\*

| All input and outputs (except $v_{NEG}$ ) with respect to $v_{SS}$ $-200$ to $\pm 0.30$ |

|-----------------------------------------------------------------------------------------|

| V <sub>NEG</sub> with respect to V <sub>SS</sub> 40V                                    |

| Storage temperature (No Data Retention)65° C to +150° C                                 |

| Storage temperature (with Data Retention)                                               |

| Operating                                                                               |

| Innowered                                                                               |

\* Exceeding these ratings could cause permanent damage to the device. This is a stress rating only and functional operation of this device at these conditions is not implied—operating ranges are specified in Standard Conditions. Exposure to absolute maximum rating conditions for extended periods may affect device reliability. Data labeled "typical" is presented for design guidance only and is not guaranteed.

#### Standard Conditions (unless otherwise noted)

$V_{SS}=+4.5V$  to +8.0V  $V_{SS}-V_{NEG}=-32V$  to -38V Operating Temperature  $T_A=0^{\circ}C$  to  $70^{\circ}C$

| Characteristic                        | Sym             | Min                 | Max                 | Units  | Conditions        |

|---------------------------------------|-----------------|---------------------|---------------------|--------|-------------------|

| DC CHARACTERISTICS                    |                 |                     |                     |        |                   |

| Input Logic "1"                       | V <sub>IH</sub> | V <sub>SS</sub> -2  | V <sub>ss</sub> +.3 | V      |                   |

| Input Logic "0"                       | VIL             | V <sub>ss</sub> -10 | Vss -4.1            | V      |                   |

| Input Leakage                         | IL              | _                   | 10                  | μΑ     |                   |

| Output Logic "1"                      | V <sub>он</sub> | _                   | V <sub>ss</sub> −.5 | V      | @ 0.5mA           |

| Power Supply                          | Iss             | 4                   | 20                  | mA     |                   |

| Power Dissipation                     | Pss             | 130                 | 700                 | mW     |                   |

| AC CHARACTERISTICS                    |                 |                     |                     |        |                   |

| Read Cycle Time                       | 1 –             | 130                 | _                   | μs     |                   |

| Read Access Time                      | l t₄            | -                   | 100                 | μs     | from fall of CS   |

| Memory Alteration Time                | 1 –             | 200                 |                     | ms     |                   |

| Time between Memory Alteration Cycles | tc              | 12.5                |                     | ms     |                   |

| Debounce Time for Changing Memory     | t <sub>B</sub>  | 12.5                | 37.5                | ms     |                   |

| Address Setup Time                    | ts              | 20                  | _                   | μs     |                   |

| Address Hold Time                     | t <sub>H</sub>  | 100                 | _                   | μs     |                   |

| Reset Time                            | t₀              | 2                   | 30                  | μs     | from rise of CS   |

| Input Rise & Fall Times               | _               | 0.03                | 30                  | ms     | on all inputs     |

| EAROM CHARACTERISTICS                 |                 |                     |                     |        |                   |

| Data Retention, Power Off (Storage)   |                 | 7                   | _                   | Years  | -40°C to +85°C    |

| Data Retention, Power On              | I –             | 2                   |                     | Years  | 0°C to +70°C      |

| Read Cycles Per Cell                  |                 | 10 <sup>7</sup>     | _                   | _      | no loss of data   |

| Erase/Write Cycles per Cell           | -               | 10 <sup>3</sup>     |                     | Cycles | 10 year retention |

| Erase/Write Cycles per Cell           | _               | 10⁴                 | _                   | Cycles | 1 year retention  |

NOTE 1: Data will be valid until the next positive  $\overline{\text{CS}}$  transition or until initiation of an alteration cycle.

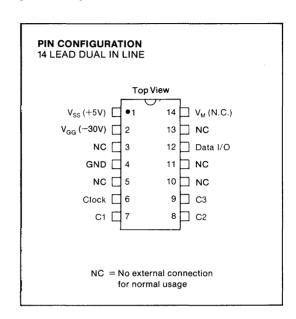

#### 700 Bit Serial Electrically Alterable Read Only Memory

#### **FEATURES**

- 50 Word x 14 Bit Organization

- Addressing by Two Consecutive One-of-Ten Codes

- Word Alterable

- 10 Year Data Storage

- TTL Compatible Signal Levels

- Write/Erase Time: 10ms

#### DESCRIPTION

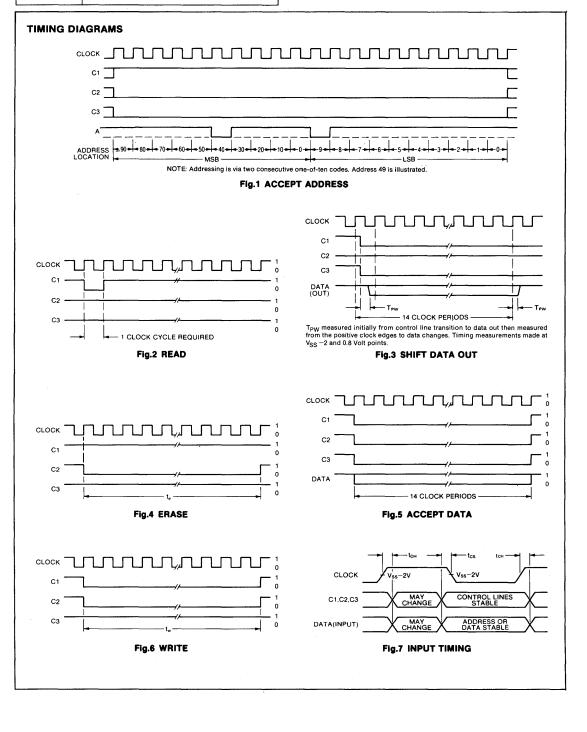

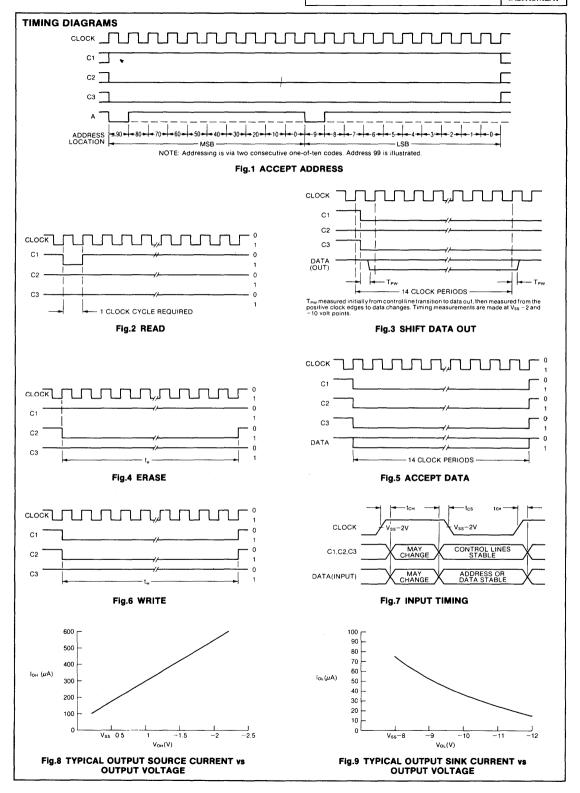

The ER1451 is a serial input/output 700 bit electrically erasable and reprogramable ROM, organized as 50 words of 14 bits each. Data and address are communicated in serial form via a one-pin bidirectional bus. Its operation is similar to the ER1400 in all respects, except that it has only half the memory capacity. The address, in the form of two consecutive one-of-ten codes, is shifted in with the first ten bits indicating the MSD. Address 49 is the highest valid address. For this reason during the first five clock cycles of an ACCEPT ADDRESS function the data input is ignored.

Mode selection is by a 3 bit code applied to C1, C2 and C3.

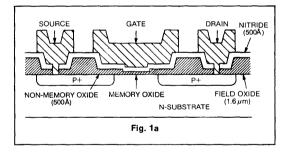

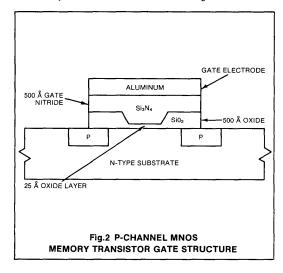

Before writing, a selected location must be preconditioned by an Erase operation. Data is then stored by internal negative writing pulses that selectively tunnel charge into the oxide-nitride interface of the gate insulator of the 700 MNOS memory transistors. When the writing voltage is removed the charge trapped at the interface is manifested as a negative shift in the threshold voltage of the selected memory transistors.

#### **PIN FUNCTIONS**

| Name            | Function                                                                                                                                                                                                 |           |           |                                                                                                                                                             |  |  |  |  |  |  |

|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Data            | In the Accept Address and Accept Data modes, this pin is an input pin for address and data respectively. When outputting data it has TTL drive capability, while in all other modes it is left floating. |           |           |                                                                                                                                                             |  |  |  |  |  |  |

| V <sub>M</sub>  | Used for testing purposes only. Must be left unconnected for normal operation.                                                                                                                           |           |           |                                                                                                                                                             |  |  |  |  |  |  |

| V <sub>ss</sub> | Chip                                                                                                                                                                                                     | subst     | rate. N   | ormally connected to +5V                                                                                                                                    |  |  |  |  |  |  |

| V <sub>GG</sub> | DC:                                                                                                                                                                                                      | supply.   | Norma     | ally connected to -30 Volt supply.                                                                                                                          |  |  |  |  |  |  |

| Clock           | Tim                                                                                                                                                                                                      | ing refe  | erence.   | Required for all operations. May be left at logic one when device is in standby.                                                                            |  |  |  |  |  |  |

| C1, C2, C3      | Mod                                                                                                                                                                                                      | le cont   | rol pins  | s. Their operation is as follows:                                                                                                                           |  |  |  |  |  |  |

|                 | <u>C1</u>                                                                                                                                                                                                | <u>C2</u> | <u>C3</u> | Function                                                                                                                                                    |  |  |  |  |  |  |

|                 | 1                                                                                                                                                                                                        | 1         | 1         | Standby—The output buffer is left floating. If the clock is maintained, the contents of the Address and Data Registers will remain unchanged.               |  |  |  |  |  |  |

|                 | 1                                                                                                                                                                                                        | 0         | 0         | Accept Address—Data presented at the I/O pin is shifted into the Address Register with each clock pulse. Addressing is by two consecutive one-of-ten codes. |  |  |  |  |  |  |

| 1               | 0                                                                                                                                                                                                        | 1         | 1         | Read—The address word is read from memory into the data register.                                                                                           |  |  |  |  |  |  |

|                 | .0                                                                                                                                                                                                       | 1         | 0         | Shift Data Out—The output driver is enabled and the contents of the Data Register are shifted ou one bit with each clock pulse.                             |  |  |  |  |  |  |

|                 | 1                                                                                                                                                                                                        | 0         | 1         | Erase—The word stored at the addressed location is erased to all zeroes.                                                                                    |  |  |  |  |  |  |

|                 | 0                                                                                                                                                                                                        | 0         | 0         | Accept Data—The data register accepts serial data presented at the I/O pin. The Address Registe remains unchanged.                                          |  |  |  |  |  |  |

|                 | 0                                                                                                                                                                                                        | 0         | 1         | Write—The word contained in the Data Register is written into the location designated by the Address Register.                                              |  |  |  |  |  |  |

|                 | 1                                                                                                                                                                                                        | 1         | 0         | Not Used.                                                                                                                                                   |  |  |  |  |  |  |

#### **ELECTRICAL CHARACTERISTICS**

#### Maximum Ratings\*

| 0.3V |

|------|

| -40V |

| 0° C |

|      |

| 5° C |

| 0° C |

|      |

\* Exceeding these ratings could cause permanent damage to the device. This is a stress rating only and functional operation of this device at these conditions is not implied—operating ranges are specified in Standard Conditions. Exposure to absolute maximum rating conditions for extended periods may affect device reliability. Data labeled "typical" is presented for design guidance only and is not guaranteed.

#### Standard Conditions (unless otherwise noted)

$$\begin{split} &V_{SS} = +5 \text{ Volts} \pm 5\% \quad \text{GND} = 0 \text{ Volts} \\ &V_{GG} = -30 \text{ Volts} \pm 5\% \\ &\text{Operating Temperature } T_{A} = 0^{\circ}\text{C to} + 70^{\circ}\text{C} \end{split}$$

| Characteristics                        | Sym             | Min                  | Тур** | Max                  | Units | Conditions                |

|----------------------------------------|-----------------|----------------------|-------|----------------------|-------|---------------------------|

| DC CHARACTERISTICS                     |                 |                      |       |                      |       |                           |

| Input Logic "0"                        | VIL             | V <sub>SS</sub> -15  | _     | +0.8                 | Volts |                           |

| Input Logic "1"                        | V <sub>IH</sub> | V <sub>SS</sub> -1.5 | l —   | V <sub>SS</sub> +0.3 | Volts |                           |

| Input Leakage                          | 1,              | "-                   |       | 10                   | μΑ    | $V_{IN} = -10V$           |

| Output Logic "0"                       | V <sub>ol</sub> |                      | _     | +0.4                 | Volts | I <sub>OL</sub> = 3.2mA   |

| Output Logic "1"                       | V <sub>OH</sub> | V <sub>SS</sub> -1.5 | -     | V <sub>ss</sub>      | Volts | I <sub>OH</sub> = 3.2mA   |

| Power Consumption                      | P <sub>GG</sub> |                      | _     | 300                  | mW    |                           |

| Power Supply Current                   | IGG             | _                    | _     | 8                    | mΑ    |                           |

|                                        | Iss             | -                    | -     | 8                    | mΑ    |                           |

| AC CHARACTERISTICS                     |                 |                      |       |                      |       |                           |

| Clock Frequency                        | fφ              | 10                   | 14    | 17                   | KHz   |                           |

| Clock Duty Cycle                       | Dφ              | 35                   | 50    | 65                   | %     |                           |

| Write Time                             | tw              | 10                   | 15    | 24                   | ms    |                           |

| Erase Time                             | te              | 10                   | 15    | 24                   | ms    |                           |

| Rise, Fall Time                        | tr, tf          | -                    |       | 1                    | μs    |                           |

| Control, Data Set Up Time              | tcs             | 1                    | _     | - 1                  | μs    |                           |

| Control, Data Hold Time                | t <sub>CH</sub> | 0                    |       | -                    | μs    |                           |

| Propagation Delay                      | tpw             | -                    | -     | 20                   | μs    | Load: 2 TTL gates + 100pf |

| Non-Volatile Data Storage              | Ts              | 10                   | -     | -                    | Years | See Note 1.               |

| Number of Erase/Write Cycles           | Nw              | _                    | -     | 104                  | _     | Per word. See Note 2.     |

| Number of Read Accesses Between Writes | N <sub>BA</sub> | 10 <sup>9</sup>      | -     | _                    | _     | Per word                  |

|                                        | I               | I                    | i     | l                    | L     | l                         |

<sup>\*\*</sup>Typical values are at +25° C and nominal voltages.

NOTES: 1. T<sub>S</sub> is for powered or unpowered storage.

<sup>2.</sup> N<sub>W</sub> (=10<sup>4</sup>) is a maximum for data retention times greater than 10 years. Beyond 10<sup>4</sup> reprograming cycles, there is a gradual, logarithmic reduction in retention time with 1 year being a typical value after 10<sup>5</sup> cycles.

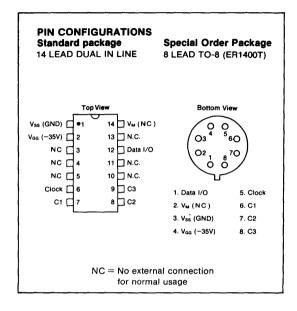

### 1400 Bit Serial Electrically Alterable Read Only Memory

#### **FEATURES**

- 100 Word x 14 Bit Organization

- Addressing by Two Consecutive One-of-Ten Codes

- Single -35 Volt Supply

- Word Alterable

- 10 Year Data Storage

- MOS Compatible Signal Levels

- Write/Erase Time: 10ms

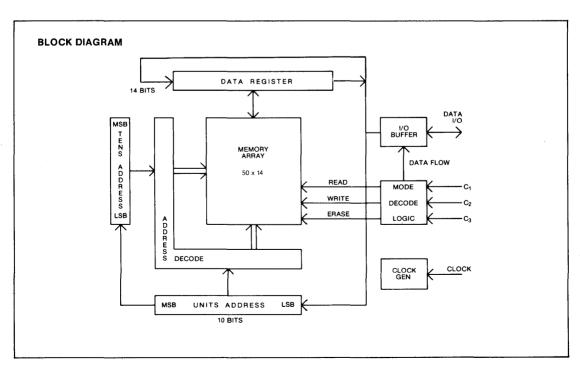

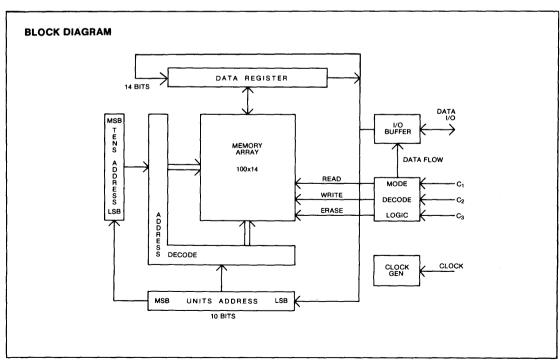

#### DESCRIPTION

The ER1400 is a serial input/output 1400 bit electrically erasable and reprogramable ROM, organized as 100 words of 14 bits each. Data and address are communicated in serial form via a one-pin bidirectional bus.

Mode selection is by a 3 bit code applied to C1, C2 and C3.

Before writing, a selected location must be preconditioned by an Erase operation. Data is then stored by internal negative writing pulses that selectively tunnel charge into the oxide-nitride interface of the gate insulator of the 1400 MNOS memory transistors. When the writing voltage is removed the charge trapped at the interface is manifested as a negative shift in the threshold voltage of the selected memory transistors.

#### **PIN FUNCTIONS**

| Name            | İ                                                 |                                                                                |           | Function                                                                                                                                                    |  |  |  |  |  |  |

|-----------------|---------------------------------------------------|--------------------------------------------------------------------------------|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Data            | In t                                              | he Acc                                                                         | ept Ac    | dress and Accept Data modes, this pin is an input pin for address and data respectively.                                                                    |  |  |  |  |  |  |

|                 | Wh                                                | en out                                                                         | putting   | data it has MOS drive capability, while in all other modes it is left floating.                                                                             |  |  |  |  |  |  |

| V <sub>M</sub>  | Use                                               | Used for testing purposes only. Must be left unconnected for normal operation. |           |                                                                                                                                                             |  |  |  |  |  |  |

| V <sub>ss</sub> | Chi                                               | p subs                                                                         | trate. I  | Normally connected to ground.                                                                                                                               |  |  |  |  |  |  |

| $V_{GG}$        | DC                                                | supply                                                                         | , Norr    | nally connected to V <sub>ss</sub> −35 Volt supply.                                                                                                         |  |  |  |  |  |  |

| Clock           | Tim                                               | ing re                                                                         | ference   | e. Required for all operations. May be left at logic zero when device is in standby.                                                                        |  |  |  |  |  |  |

| C1,C2,C3        | Mode control pins. Their operation is as follows: |                                                                                |           |                                                                                                                                                             |  |  |  |  |  |  |

|                 | <u>C1</u>                                         | <u>C2</u>                                                                      | <u>C3</u> | Function                                                                                                                                                    |  |  |  |  |  |  |

|                 | 0                                                 | 0                                                                              | 0         | Standby—the output buffer is left floating. If the clock is maintained, the contents of the Address and Data Registers will remain unchanged.               |  |  |  |  |  |  |

|                 | 0                                                 | 1                                                                              | 1         | Accept Address—Data presented at the I/O pin is shifted into the Address Register with each clock pulse. Addressing is by two consecutive one-of-ten codes. |  |  |  |  |  |  |

|                 | 1                                                 | 0                                                                              | 0         | Read—The address word is read from memory into the data register.                                                                                           |  |  |  |  |  |  |

|                 | 1                                                 | 0                                                                              | 1         | Shift Data Out—The output driver is enabled and the contents of the Data Register are shifted out one bit with each clock pulse.                            |  |  |  |  |  |  |

|                 | 0                                                 | 1                                                                              | 0         | Erase—The word stored at the addressed location is erased to all ones.                                                                                      |  |  |  |  |  |  |

|                 | 1                                                 | 1                                                                              | 1         | Accept Data—The data register accepts serial data presented at the I/O pin. The Address Register remains unchanged.                                         |  |  |  |  |  |  |

|                 | 1                                                 | 1                                                                              | 0         | Write—The word contained in the Data Register is written into the location designated by the Address Register.                                              |  |  |  |  |  |  |

|                 | 0                                                 | 0                                                                              | 1         | Not Used                                                                                                                                                    |  |  |  |  |  |  |

#### **ELECTRICAL CHARACTERISTICS**

#### Maximum Ratings\*

| All inputs and outputs (except V <sub>GC</sub> ) with respect to V <sub>SS</sub> 20V to +0.3V |

|-----------------------------------------------------------------------------------------------|

| V <sub>GG</sub> with respect to V <sub>SS</sub>                                               |

| Storage temperature (No Data Retention)65° C to +150° C                                       |

|                                                                                               |

| Storage temperature (with Data Retention)                                                     |

| Operating                                                                                     |

| Unpowered                                                                                     |

#### Standard Conditions (unless otherwise noted):

$V_{SS} = GND$  $V_{GG} = -35V \pm 8\%$

Operating Temperature  $T_A = 0$ ° C to +70° C

\* Exceeding these ratings could cause permanent damage to the device. This is a stress rating only and functional operation of this device at these conditions is not implied—operating ranges are specified in Standard Conditions. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

Data labeled "typical" is presented for design guidance only and is not guaranteed.

| Characteristics                        | Symbol          | Min                | Тур** | Max                  | Units | Conditions               |

|----------------------------------------|-----------------|--------------------|-------|----------------------|-------|--------------------------|

| DC CHARACTERISTICS                     |                 |                    |       |                      |       |                          |

| Input Logic "1"                        | VIL             | V <sub>SS</sub> 15 | _     | V <sub>SS</sub> -8   | Volts |                          |

| Input Logic "0"                        | V <sub>IH</sub> | V <sub>SS</sub> -1 | _     | V <sub>SS</sub> +0.3 | Volts |                          |

| Input Leakage                          | $I_{L}$         | _                  | _     | 10                   | μΑ    | $V_{IN} = -15V$          |

| Output Logic "1"                       | Vol             |                    | l –   | V <sub>SS</sub> -10  | Volts | Load = 1.5 Meg, 100pf    |

| Output Logic "0"                       | Voн             | V <sub>SS</sub> -1 | _     | V <sub>ss</sub> +0.3 | Volts | $I_{SOURCE} = 200 \mu A$ |

| Power Consumption                      | $P_{GG}$        | _                  | _     | 300                  | mW    | •                        |

| Power Supply Current                   | lgg             | _                  | _     | 12                   | mA    |                          |

| AC CHARACTERISTICS                     |                 |                    |       |                      |       |                          |

| Clock Frequency                        | fφ              | 10                 | 14    | 17                   | KHz   |                          |

| Clock Duty Cycle                       | $D \phi$        | 35                 | 50    | 65                   | %     |                          |

| Write Time                             | tw              | 10                 | 15    | 24                   | ms    |                          |

| Erase Time                             | te              | 10                 | 15    | 24                   | ms    |                          |

| Rise, Fall Time                        | tr, tf          | _                  |       | 1                    | μs    |                          |

| Control, Data Set Up Time              | tcs             | 1                  | _     | _                    | μs    |                          |

| Control, Data Hold Time                | tсн             | 0                  | _     |                      | μs    |                          |

| Propagation Delay                      | tpw             | _                  | _ :   | 20                   | μs    | Load - 1 Meg. 100pf      |

| Non-Volatile Data Storage              | Ts              | 10                 | _     |                      | Years | See Note 1.              |

| Number of Erase/Write Cycles           | Nw              | _                  |       | 10⁴                  | _     | Per word. See Note 2.    |

| Number of Read Accesses Between Writes |                 | 10 <sup>9</sup>    |       | _                    | 1 – 1 | Per word                 |

<sup>\*\*</sup> Typical values are at +25° C and nominal voltages.

NOTE 1: T<sub>s</sub> is for powered or unpowered storage.

NOTE 2: N<sub>W</sub> (=10<sup>4</sup>) is a maximum for data retention times greater than 10 years. Beyond 10<sup>4</sup> reprograming cycles, there is a gradual, logarithmic reduction in retention time with 1 year being a typical value after 10<sup>5</sup> cycles.

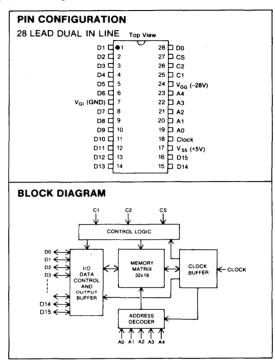

#### 512 Bit Electrically Alterable Read Only Memory

- 32 Word x 16 Bit Organization

- 5 Bit Binary Addressing

- +5, -28V Power Supplies

- Word Alterable

- 10 Year Data Storage for ER2051 (at +70°C)

- 1 Year Data Storage for ER2051 IR (at +85°C) and ER2051 HR (at +125°C)

- TTL Compatibility with Pull-Up Resistors on Inputs

- Tri-State Outputs

- Read Time: 1µs (ER2051), 2µs (ER2051 IR and ER2051 HR)

- Write/Erase Time: 50ms (ER2051), 100ms (ER2051 HR)

- No Voltage Switching Required

- Chip Select

- Two Extended Temperature Ranges:

- -40°C to +85°C (Industrial) ER2051 IR

- -55°C to +125°C (Hi-Rel) ER2051 HR

#### DESCRIPTION

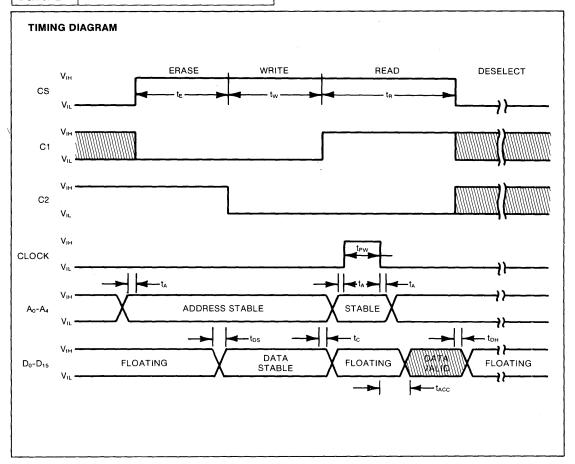

The ER2051, ER2051 IR and ER2051 HR are fully decoded 32 x 16 electrically erasable and reprogramable ROMs. Write, erase, and read voltages are switched internally via a 2-bit code applied to C1 and C2.

Data is stored by applying negative writing pulses that selectively tunnel charge into the oxide-nitride interface of the gate insulator of the 512 MNOS memory transistors. When the writing voltage is removed the charge trapped at the interface is manifested as a negative shift in the threshold voltage of the selected memory transistors.

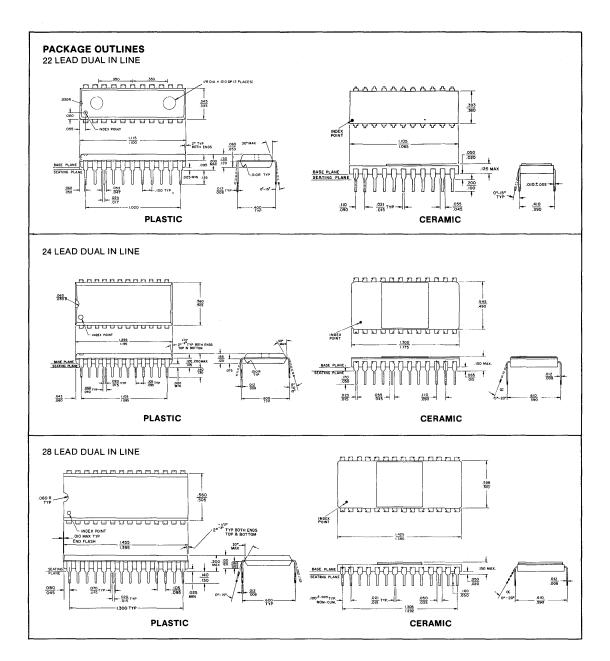

The EAROM may be operated with the  $V_{SS}$  power supply between +5V and +10Volts, as long as the  $V_{SS}$ — $V_{GG}$  always equals 33 Volts. Thus,  $V_{SS}$  can be +5Volts for TTL compatibility or up to +10Volts for CMOS compatibility, if  $V_{GG}$  is appropriately adjusted. The ER2051 IR and ER2051 HR are screened to Mil Std. 883B/method 5004.1/level B, pre-cap visual inspection, environmental testing, burn-in and external visual. They are available in 28 lead ceramic dual in line packages.

#### **OPERATION**

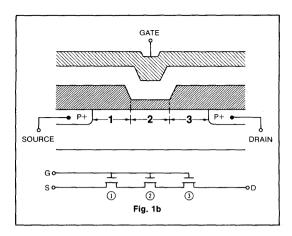

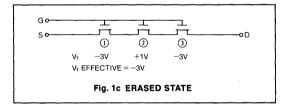

Data is stored in a two transistor memory cell. After the cell is preconditioned by an erase signal (which causes a positive shift in the threshold of both transistors), data is written into one of the transistors making its threshold more negative. A sensing flip flop is used to read the memory cell and presents a logic high or low to the output depending on which transistor is "written."

It is important to note two things: first, that an erase is required before a wire to precondition the cell, and second, that after an erase, both transistors will have the same threshold voltage and valid data will not be present at the output.

The ER2051, ER2051 IR and ER2051 HR EAROMs use dynamic, edge triggered circuits internally. This requires either a mode change, a clock or a transition of the chip select between successive operations. Thus successive operations in the same mode must be separated by transitions of one of these four lines. Clock pulses are not normally required during erase or write operations, but are needed for successive operations if the chip select is held high, i.e., applications where one EAROM is used.

#### **PIN FUNCTIONS**

| Name                            | Function                                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |  |

|---------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| A <sub>0</sub> -A <sub>4</sub>  | 5-Bit Word Address                                                                                                                                                                                                                                                                                                           |  |  |  |  |  |  |

| D <sub>0</sub> -D <sub>15</sub> | Data input and output pins                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |  |

| CS                              | Chip Select. Chip selected at logic "1". When chip select is at logic "0", outputs are open circuit, read, write and erase are disabled. Power is reduced.                                                                                                                                                                   |  |  |  |  |  |  |

| C1, C2                          | Mode Control Inputs  C1 C2  0 1 Erase Mode: stored data is erased at addressed location.  1 Don't Care Read Mode: addressed data read after clock pulse. Output data retained at output pins until chip deselected or control lines switched.  0 0 Write Mode: input data written at addressed location. Clock not required. |  |  |  |  |  |  |

| CLK                             | Clock input. Pulse to logic "1" for read operation.                                                                                                                                                                                                                                                                          |  |  |  |  |  |  |

| $V_{SS}$                        | Substrate supply. Normally at +5 volts.                                                                                                                                                                                                                                                                                      |  |  |  |  |  |  |

| $V_{GI}$                        | Ground Input.                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |  |

| V <sub>GG</sub>                 | Power Supply Input. Normally at -28 volts.                                                                                                                                                                                                                                                                                   |  |  |  |  |  |  |

#### **ELECTRICAL CHARACTERISTICS**

#### Maximum Ratings\*

All input and outputs (with respect to V<sub>SS</sub>) ..... -35V to +0.3V Storage temperature ..... -65° C to +150° C Soldering temperature of leads (10 seconds) ..... +300° C

#### Standard Conditions (for TTL compatibility)

$V_{SS} = +5V \pm 5\%$  $V_{GG} = -28V \pm 5\%$

$v_{GG} = 200 \pm 0$   $v_{GI} = GND$

Operating Temperature  $T_A = 0^{\circ} \text{C to } +70^{\circ} \text{C for } \text{ER2051}$

$T_A = -40^{\circ} \text{C to } +85^{\circ} \text{C for ER2051 IR}$

$T_A = -55^{\circ} \text{ C to } + 125^{\circ} \text{ C for ER2051 HR}$

Output Load = 100pf, 1 TTL load

\* Exceeding these ratings could cause permanent damage to the device. This is a stress rating only and functional operation of this device at these conditions is not implied—operating ranges are specified in Standard Conditions. Exposure to absolute maximum rating conditions for extended periods may affect device reliability. Data labeled "typical" is presented for design guidance only and is not guaranteed.

|                                  |                                | E                    | R2051  |          | ER2051               | IR/ER  | 2051 HR  |       |                                                   |

|----------------------------------|--------------------------------|----------------------|--------|----------|----------------------|--------|----------|-------|---------------------------------------------------|

| Characteristics                  | Sym                            | Min.                 | Тур.** | Max.     | Min.                 | Тур.** | Max.     | Units | Conditions                                        |

| DC CHARACTERISTICS               |                                |                      |        |          |                      |        |          |       |                                                   |

| Input Logic "1"                  | VIH                            | V <sub>SS</sub> -1.5 |        | Vss +0.3 | V <sub>ss</sub> -1.5 |        | Vss +0.3 | v     |                                                   |

| Input Logic "0"                  | VIL                            | Vss -15              |        | 0.8      | V <sub>ss</sub> -10  |        | 0.6      | · v   | i                                                 |

| Output Logic "1"                 | V <sub>он</sub>                | V <sub>SS</sub> -1.5 |        | _        | V <sub>ss</sub> -1.5 | i — I  | _        | V     | $I_{OH} = 100 \mu A$                              |

| Output Logic "0"                 | Vol                            | -                    | -      | 0.6      |                      | _      | 0.6      | ν     | $I_{OL} = 1.6 \text{mA for } V_{SS} = 5 \text{V}$ |

| Input Leakage                    | ΙL                             |                      | 2      | 10       | _                    | 2      | 10       | μΑ    | $V_{IN} = V_{SS} - 15$                            |

| Output Leakage                   | Io                             | - 1                  | 2      | 10       |                      | 2      | 10       | μA    | Chip deselected                                   |

| Power Supply Current             |                                |                      |        |          |                      | ]      | Į        |       |                                                   |

| Read                             | $I_{GG}$                       |                      | _      | 14       | _                    |        | 18       | mA    | 1                                                 |

| Write                            | $I_{GG}$                       |                      | _      | 11       |                      | _      | 15       | mA i  | I <sub>GG</sub> returned                          |

| Erase                            | $I_{GG}$                       | - '                  | _      | 11       | _                    | _      | 15       | mA .  | through Vss                                       |

| Deselected                       | $I_{GG}$                       |                      | _      | 9        | _                    |        | 12       | mA    |                                                   |

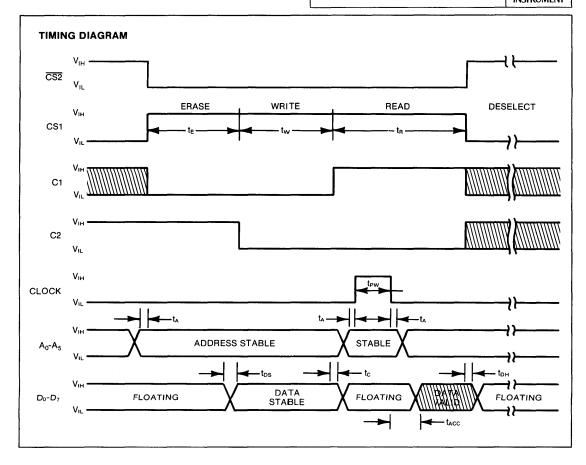

| AC CHARACTERISTICS               |                                | 1                    |        |          |                      | 1      |          |       |                                                   |

| Access Time                      | tACC                           | _                    | _      | 1        | _                    | l — i  | 2        | μs    |                                                   |

| Clock Pulse width                | tew                            | 2                    | -      | 20       | 2                    | _      | 20       | μs    |                                                   |

| Erase Cycle Time                 | t <sub>E</sub>                 | 50                   |        | 200      | 100                  | 1 – 1  | 200      | ms    |                                                   |

| Write Cycle Time                 | tw                             | 50                   | _      | 200      | 100                  |        | 200      | ms    |                                                   |

| Read Cycle Time                  | t <sub>R</sub>                 | 3.5                  |        | 24       | 4.5                  | _      | 25       | μs    |                                                   |

| Address to Clock Time            | t <sub>A</sub>                 | 50                   | _      | _        | 50                   |        | _        | ns    |                                                   |

| Data Set Up Time                 | tos                            | 50                   |        | _        | 50                   | l — i  | _        | ns    |                                                   |

| Data Hold Time                   | toн                            | 50                   | _      |          | 50                   | -      |          | ns    |                                                   |

| Control to Address & Data Change | tc                             | 0                    |        | _        | 0                    | _      | _        | ns    |                                                   |

| Number of Reads/Word Refresh     | NRA                            | 10''                 | _      | _        | 10''                 |        | _        |       |                                                   |

| Number of Erase/Write Cycles     | Nw                             | 10 <sup>6</sup>      | _      | _ :      | 10 <sup>5</sup>      | -      |          |       |                                                   |

| Input Capacitance (All Pins)     | C <sub>10</sub>                | - 1                  | 8      | 15       |                      | 8      | 15       | pf    |                                                   |

| Unpowered Data Storage Time      | ts                             | 10                   | -      | -        | 1                    | _      | _        | Years | at max temperature                                |

| Power Dissipation Read Cycle     | Po                             | -                    | 450    | 500      | _                    | 450    | 500      | mW    | at 25°C $V_{SS} = +5$ , $V_{GG} = -29$            |

|                                  | PD                             | not                  | applic | able     |                      | _      | 500      | mW    | at 125°C $V_{SS} = +5$ , $V_{GG} = -29$           |

| !                                | PD                             |                      | applic |          |                      | _      | 600      | mW    | at $-55^{\circ}$ C $V_{SS} = +5$ , $V_{GG} = -29$ |

| Pulse Rise, Fall Time            | t <sub>R1</sub> t <sub>F</sub> | 10                   | _      | 100      | 10                   | -      | 100      | ns    |                                                   |

<sup>\*\*</sup>Typical values are at +25°C and nominal voltages.

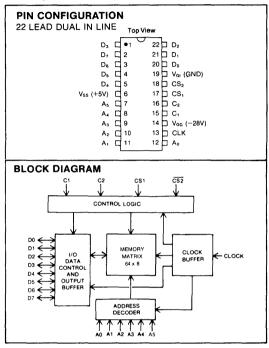

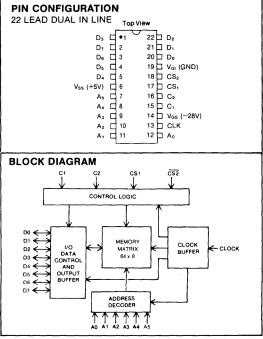

#### 512 Bit Electrically Alterable Read Only Memory

#### **FEATURES**

- 64 Word x 8 Bit Organization

- 6 Bit Binary Addressing

- +5, -28V Power Supplies

- Word Alterable

- 10 Year Data Storage for ER2055 (at +70°C)

- 1 Year Data Storage for ER2055 IR (at +85°C) and ER2055 HR (at +125°C)

- TTL Compatible with Pull-Up Resistors on Inputs

- Tri-State Outputs

- Read Time: 2µs (ER2055), 4µs (ER2055 IR and ER2055 HR)

- Write/Erase Time: 50ms (ER2055), 100ms (ER2055 HR)

- No Voltage Switching Required

- 2 Chip Selects

- Two Extended Temperature Ranges:

- -40°C to +85°C (Industrial) ER2055 IR

- -55°C to +125°C (Hi-Rel) ER2055 HR

#### DESCRIPTION

The ER2055 is a fully decoded 64 x 8 electrically erasable and reprogramable ROM. Write, erase, and read voltages are switched internally via a 2-bit code applied to C1 and C2.

Data is stored by applying negative writing pulses that selectively tunnel charge into the oxide-nitride interface of the gate insulator of the 512 MNOS memory transistors. When the writing voltage is removed the charge trapped at the interface is manifested as a negative shift in the threshold voltage of the selected memory transistors.

#### **OPERATION**

Data is stored in a two transistor memory cell. After the cell is preconditioned by an erase signal (which causes a positive shift in the threshold of both transistors), data is written into one of the transistors making its threshold more negative. A sensing flip flop is used to read the memory cell and presents a logic high or low to the output depending on which transistor is "written".

The ER2055 EAROM may be operated with  $V_{SS}$  between  $\pm 5$  and  $\pm 10$  volts for either TTL or CMOS compatibility. The negative power supply,  $V_{GG}$ , should be adjusted so that the difference between  $V_{SS}$  and  $V_{GG}$  is always 33 volts.

It is important to note two things: first, that an erase is required before a write to precondition the cell, and second, that after an erase, both transistors will have the same threshold voltage and valid data will not be present at the output.

The ER2055 EAROM uses dynamic edge triggered circuits internally. This requires either a mode change, a clock or a transition of the chip selects between successive operations. Thus successive operations in the same mode must be separated by transition of one of these four lines. Clock pulses are not normally required during erase or write operations, but are needed for successive operations if the chip is continuously selected, i.e., applications where one EAROM is used.

The ER2055IR and ER2055HR are screened to Mil Std. 883B/method 5004. 1/level B, pre-cap visual inspection, environmental testing, burn-in and external visual. They are available in 28 lead ceramic dual in-line packages.

#### **PIN FUNCTIONS**

| Name                           | Function                                                                                                                                                                                                                                                                                            |

|--------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A <sub>0</sub> -A <sub>5</sub> | 6-Bit Word Address                                                                                                                                                                                                                                                                                  |

| D <sub>0</sub> -D <sub>7</sub> | Data input and output pins                                                                                                                                                                                                                                                                          |

| CS1, CS2                       | Chip Selects Chip selected at logic "1" on CS1 and logic "0" on CS2. When chip is not selected, outputs are open circuit, read, write and erase are disabled. Power is reduced.                                                                                                                     |

| C1, C2                         | Mode Control Inputs                                                                                                                                                                                                                                                                                 |

|                                | C1 C2 0 1 Erase Mode: stored data is erased at addressed location. 1 Don't Care Read Mode: addressed data read after clock pulse. Output data retained at output pins until chip deselected or control lines switched. 0 0 Wite Mode: input data written at addressed location. Clock not required. |

| CLK                            | 0 0 Write Mode: input data written at addressed location. Clock not required.  Clock Input. Pulse to logic "1" for read operation.                                                                                                                                                                  |

| V <sub>SS</sub>                | Substrate supply. Normally at +5 volts.                                                                                                                                                                                                                                                             |

| $V_{GI}$                       | Ground Input.                                                                                                                                                                                                                                                                                       |

| $V_{GG}$                       | Power Supply Input. Normally at -28 volts.                                                                                                                                                                                                                                                          |

#### **ELECTRICAL CHARACTERISTICS**

#### Maximum Ratings\*

All inputs and outputs (with respect to  $V_{SS}$ ).........-35V to +0.3V Storage temperature .......-65° C to +150° C Soldering temperature of leads (10 seconds) .......+300° C

#### Standard Conditions (for TTL Compatibility)

$V_{SS} = +5V \pm 5\%$

$V_{GG} = -28V \pm 5\%$

$V_{GI} = GND$

Operating Temperature  $T_A = 0^{\circ} C$  to  $+70^{\circ} C$  for ER2055

$T_A = -40^{\circ} \text{C to } +85^{\circ} \text{C for ER2055IR}$

$T_A = -55^{\circ} \text{ C to } + 125^{\circ} \text{ C for ER2055HR}$

Output Load = 100pf, 1 TTL load

\* Exceeding these ratings could cause permanent damage to the device. This is a stress rating only and functional operation of this device at these conditions is not implied—operating ranges are specified in Standard Conditions. Exposure to absolute maximum rating conditions for extended periods may affect device reliability. Data labeled "typical" is presented for design guidance only and is not guaranteed.

|                                  |                                |                      | ER205    | 5        | ER2055               | IR/ER2   | 055 HR               |       |                                                           |

|----------------------------------|--------------------------------|----------------------|----------|----------|----------------------|----------|----------------------|-------|-----------------------------------------------------------|

| Characteristics                  | Sym                            | Min.                 | Typ.**   | Max.     | Min.                 | Тур.**   | Max.                 | Units | Conditions                                                |

| DC CHARACTERISTICS               |                                |                      |          |          |                      |          |                      |       |                                                           |

| Input Logic "1"                  | VIH                            | V <sub>ss</sub> -1.5 | _        | Vss +0.3 | V <sub>SS</sub> -1.5 | l —      | V <sub>ss</sub> +0.3 | V     |                                                           |

| Input Logic "0"                  | VIL                            | Vss -15              | l —      | 0.8      | V <sub>ss</sub> -10  | l —      | 0.6                  | V     |                                                           |

| Output Logic "1"                 | VoH                            | Vss -1.5             | _        | _        | V <sub>SS</sub> -1.5 | _        | _                    | V     | $I_{OH} = 100 \mu A$                                      |

| Output Logic "0"                 | Vol                            | _                    |          | 0.6      |                      | -        | 0.6                  | V     | $I_{OL} = 1.6 \text{mA} \text{ for } V_{SS} = 5 \text{V}$ |

| Input Leakage                    | ΙL                             |                      | 2        | 10       | _                    | 2        | 10                   | μΑ    | $V_{IN} = V_{SS} - 15$                                    |

| Output Leakage                   | Io                             | _                    | 2        | 10       | _                    | 2        | 10                   | μΑ    | Chip deselected                                           |

| Power Supply Current             |                                |                      |          |          |                      |          |                      |       |                                                           |

| Read                             | $I_{GG}$                       | _                    | 8        | 10       | _                    | 8        | 18                   | mA    | Iss approx Igg                                            |

| Write                            | $I_{GG}$                       | _                    | 6        | 7        | _                    | 6        | 9                    | mA    | Iss approx Igg                                            |

| Erase                            | $I_{GG}$                       | _                    | 4        | 7        | _                    | 6        | 8                    | mΑ    | Iss approx Igg                                            |

| Deselected                       | $I_{GG}$                       | -                    | 4        | 7        | _                    | 4        | 6                    | mA    | I <sub>ss</sub> approx I <sub>GG</sub>                    |

| AC CHARACTERISTICS               |                                |                      |          |          |                      |          |                      |       |                                                           |

| Access Time                      | tACC                           | _                    | l —      | 2        |                      |          | 4                    | μs    |                                                           |

| Clock Pulse Width                | tew                            | 2                    | _        | 20       | 2                    | l —      | 20                   | μs    |                                                           |

| Erase Cycle Time                 | t∈                             | 50                   | l —      | 200      | 100                  |          | 200                  | ms    |                                                           |

| Write Cycle Time                 | tw                             | 50                   | _        | 200      | 100                  | l —      | 200                  | ms    |                                                           |

| Read Cycle Time                  | t <sub>R</sub>                 | 5                    | —        | 24       | 6                    | l —      | 25                   | μs    |                                                           |

| Address to Clock Time            | tA                             | 50                   | l —      | -        | 50                   |          | - 1                  | ns    |                                                           |

| Data Set Up Time                 | tos                            | 50                   |          |          | 50                   | l —      | -                    | ns    |                                                           |

| Data Hold Time                   | t <sub>DH</sub>                | 50                   | l —      | -        | 50                   | l —      | -                    | ns    |                                                           |

| Control to Address & Data Change | tc                             | 0                    | <u> </u> | _        | 0                    | —        |                      | ns    |                                                           |

| Number of Reads/Word Refresh     | N <sub>RA</sub>                | 1011                 | —        | -        | 1011                 | —        | _                    |       |                                                           |

| Number of Erase/Write Cycles     | Nw                             | 10 <sup>6</sup>      | —        | -        | 10 <sup>5</sup>      | -        | -                    | _     |                                                           |

| Input Capacitance (All Pins)     | Cio                            |                      | 6        | 10       | _                    | 6        | 10                   | pf    |                                                           |

| Unpowered Data Storage Time      | ts                             | 10                   | -        | -        | 1                    | -        | -                    | Years | at max temperature                                        |

| Power Dissipation Read Cycle     | PD                             |                      | 450      | 500      | -                    | 450      | 500                  | mW    | at 25° C $V_{SS} = +5$ , $V_{GG} = -29$                   |

|                                  | $P_D$                          | ľ                    | applica  |          | _                    | l —      | 500                  | mW    | at 125°C $V_{SS} = +5$ , $V_{GG} = -29$                   |

|                                  | Pb                             | not a                | applica  | ible     | _                    | <u> </u> | 600                  | mW    | at $-55^{\circ}$ C $V_{SS} = +5$ , $V_{GG} = -29$         |

| Pulse Rise, Fall Time            | t <sub>R1</sub> t <sub>F</sub> | 10                   | _        | 100      | 10                   | -        | 100                  | ns    |                                                           |

<sup>\*\*</sup>Typical values are at +25°C and nominal voltages.

. .

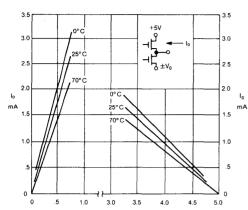

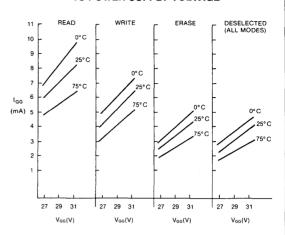

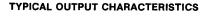

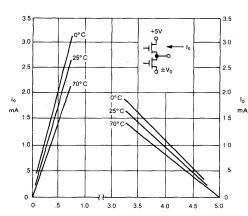

## TYPICAL SUPPLY CURRENT VS POWER SUPPLY VOLTAGE

#### PRELIMINARY INFORMATION

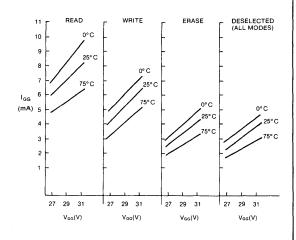

#### Word Alterable 1K Bit Electrically Erasable Programable ROM

#### **FEATURES**

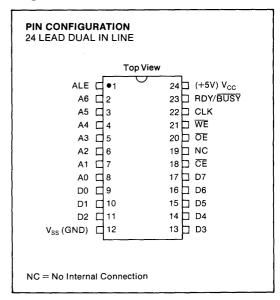

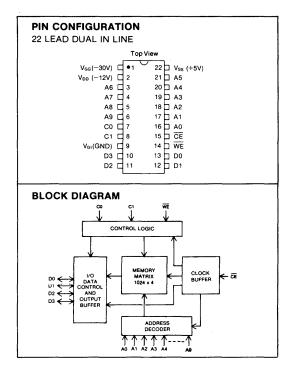

- 1024 Bits, Organized 128 x 8

- N-Channel Si-Gate SNOS Technology

- +5V Operation in All Modes; No High Voltages

- Fully TTL Compatible Inputs and Outputs

- On-Chip Latching of Addresses and Data

- Self-Timing, Processor Transparent Programing Mode with RDY/BUSY Signal

- Address and Data Buses may be used Separately or Multiplexed

- CE and OE Inputs to Avoid Bus Contention

- Word Alterable

- Read Access time of Less Than 200ns

- 10 Years' Data Retention over Temperature Range of -40° to +85° C

- Unlimited Read Accesses

#### DESCRIPTION

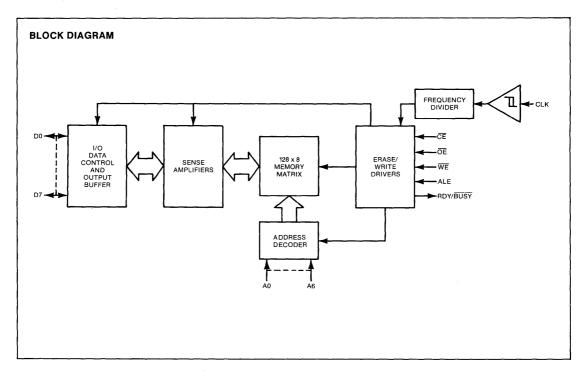

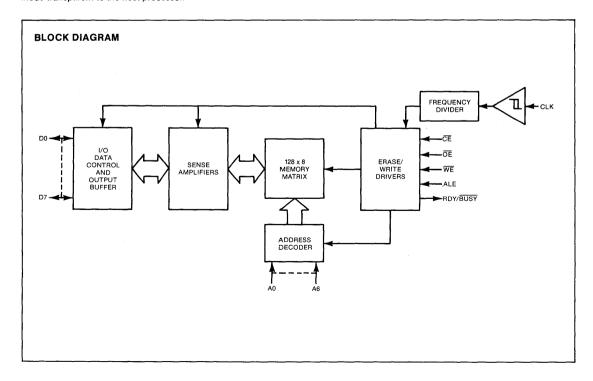

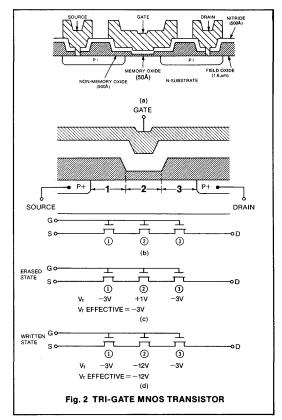

The ER5901 is a high speed electrically word erasable memory manufactured in the General Instrument proven SNOS technology. The key features of this device are its +5V only operation and microprocessor compatible architecture which allows the ER5901 to be accessed from the system bus in the same way as a static RAM. Internal memory management has been incorporated in this device. On-board latching of address and data lines in the reprograming mode, and busy signal (RDY/BUSY) output make this mode transparent to the host processor.

#### GENERAL INSTRUMENT

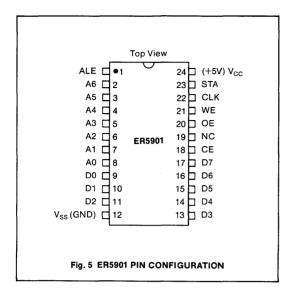

#### ER5901 = ER5901IR = ER5901HR

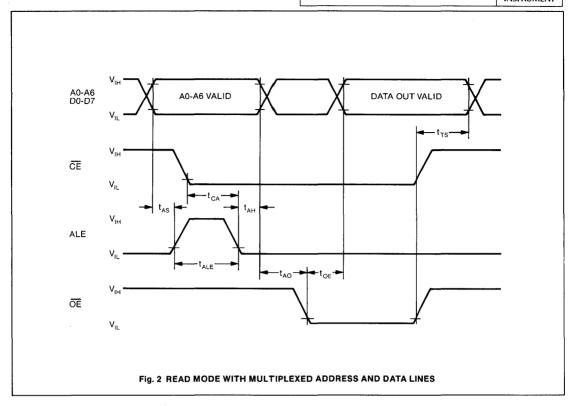

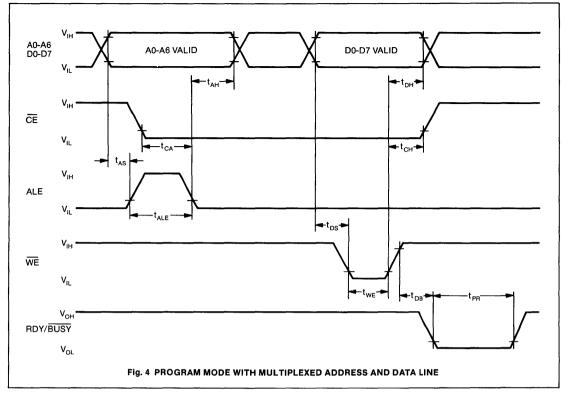

An ADDRESS LATCH ENABLE (ALE) input is provided so that memory may be used with a multiplexed address and data bus. When this feature is not required, ALE may be tied to WE.

Bus contention problems are minimized by twin line control provided by CHIP ENABLE ( $\overline{CE}$ ) and OUTPUT ENABLE ( $\overline{OE}$ ).

By virtue of the on-chip reprograming control and timing of the ER5901, a minimum amount of servicing is required from a host microprocessor or microcomputer.

The user may select one of five operating modes:

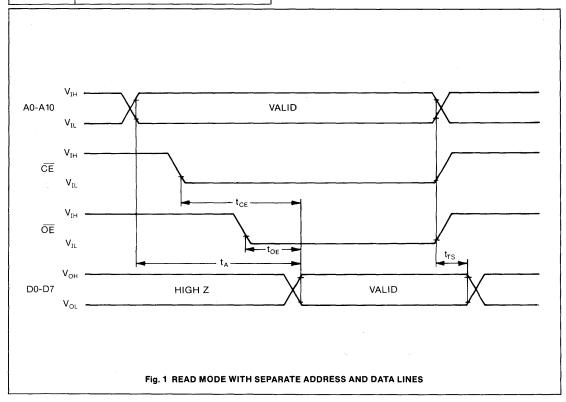

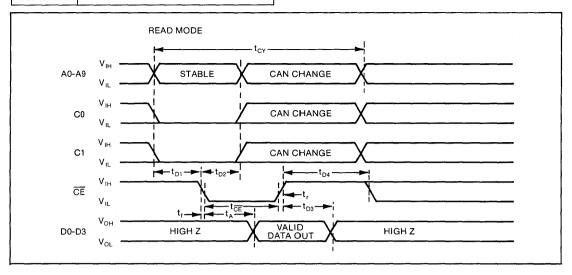

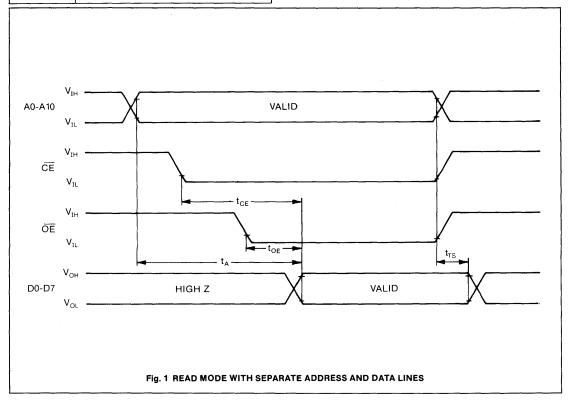

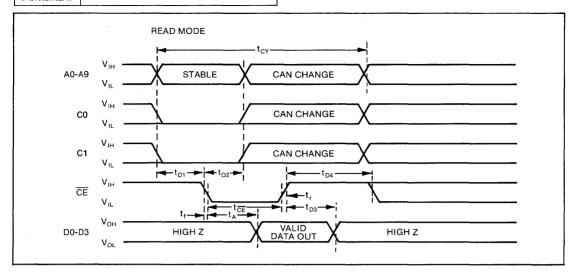

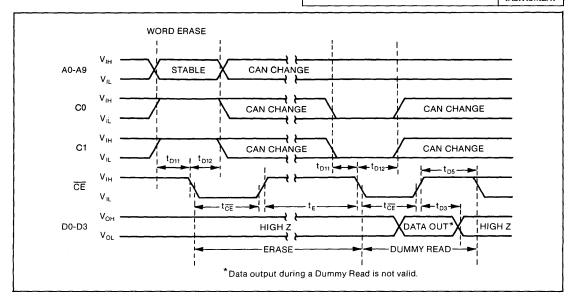

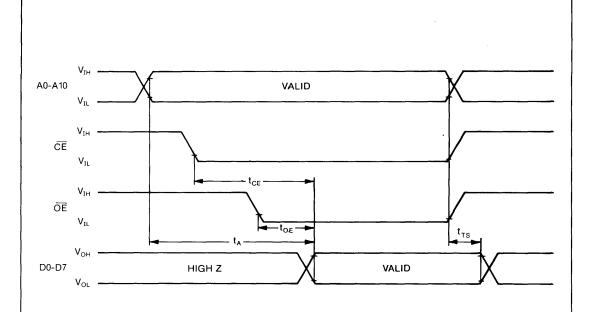

- 1. READ with separate address and data lines.

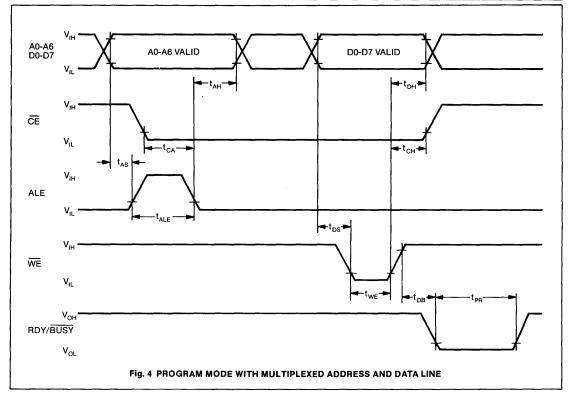

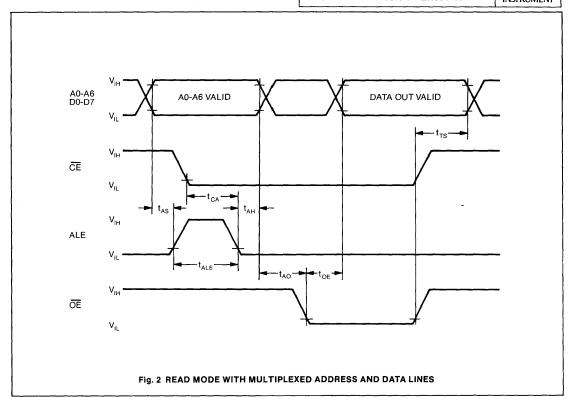

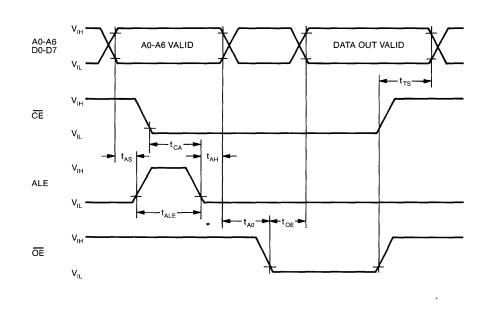

- 2. READ with multiplexed address and data lines.

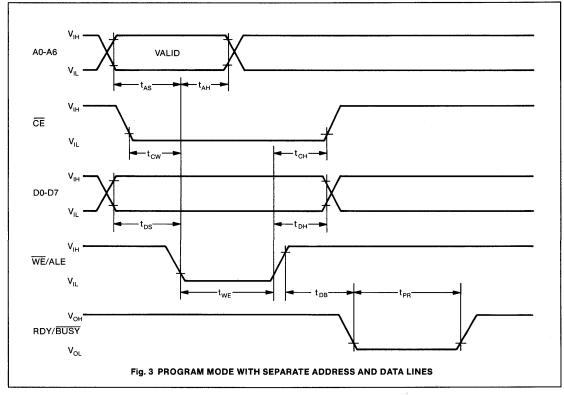

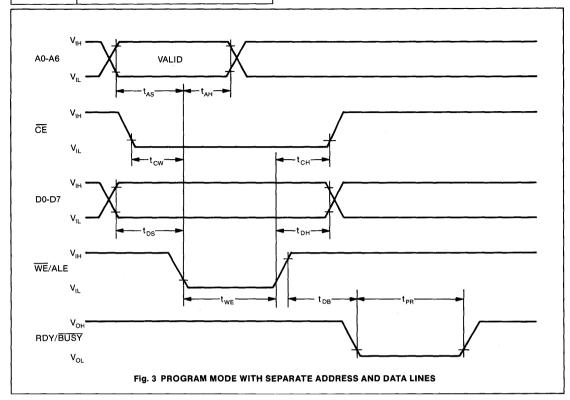

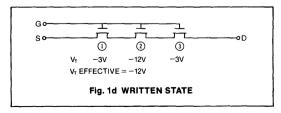

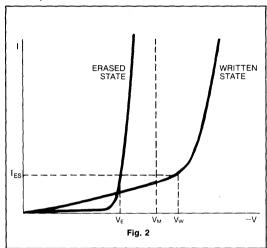

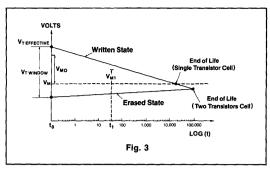

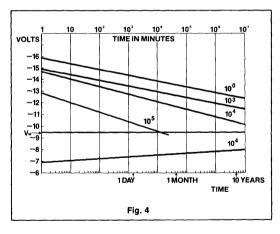

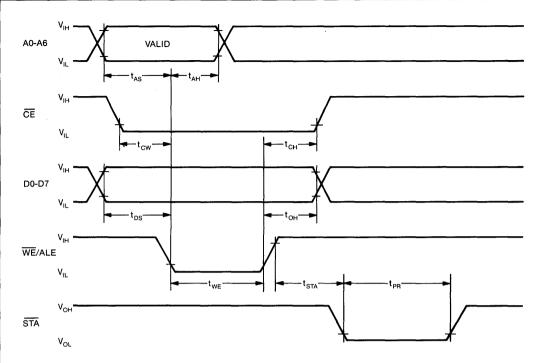

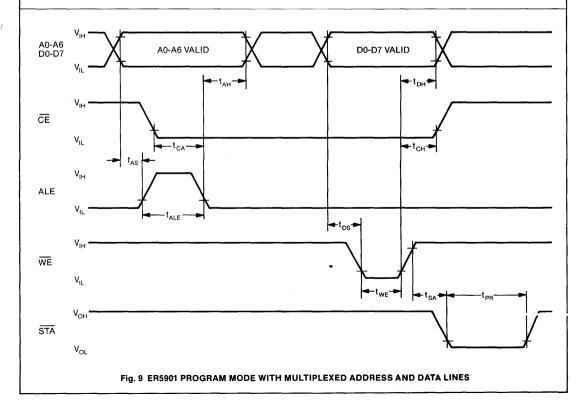

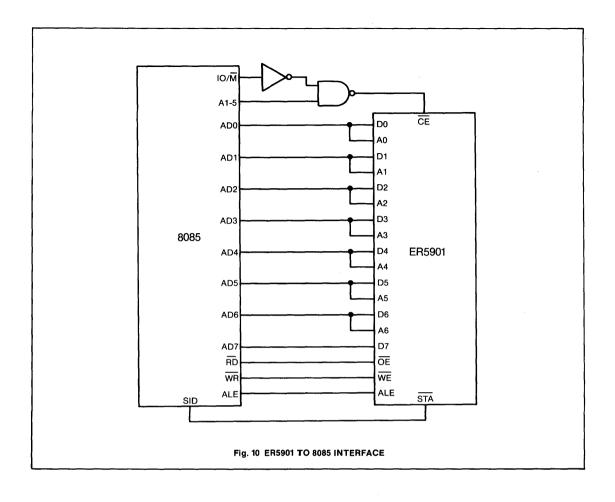

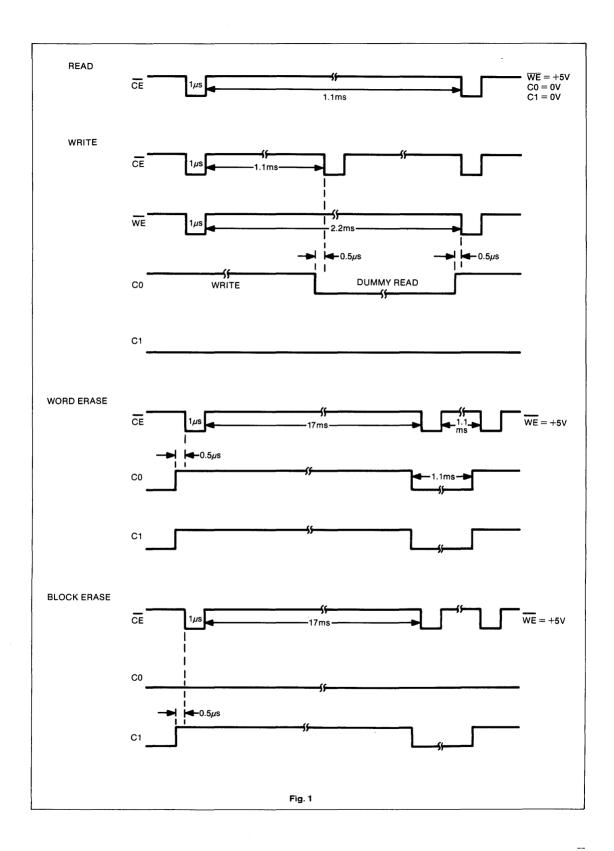

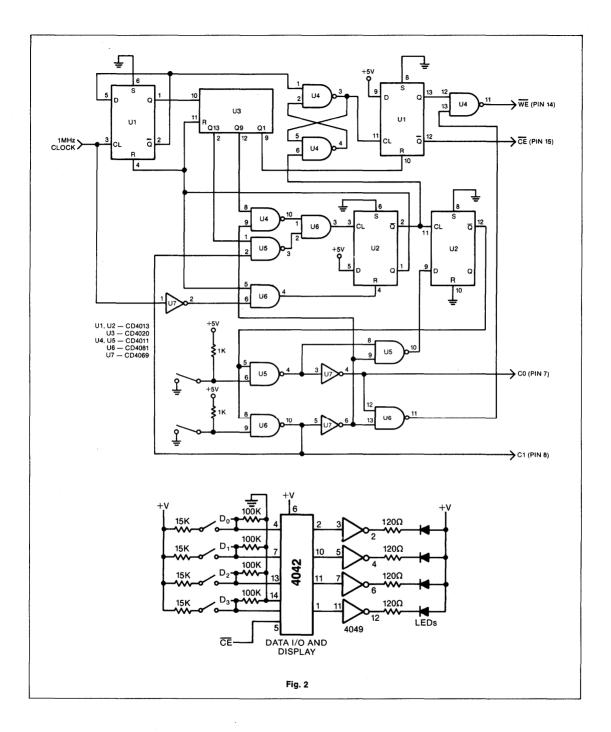

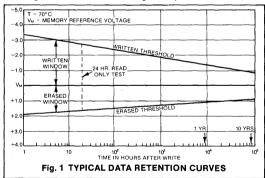

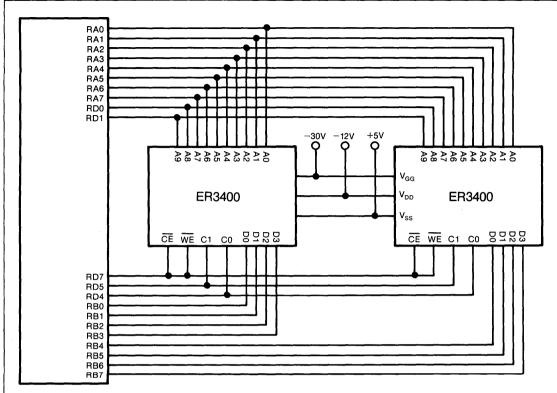

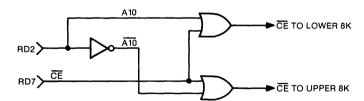

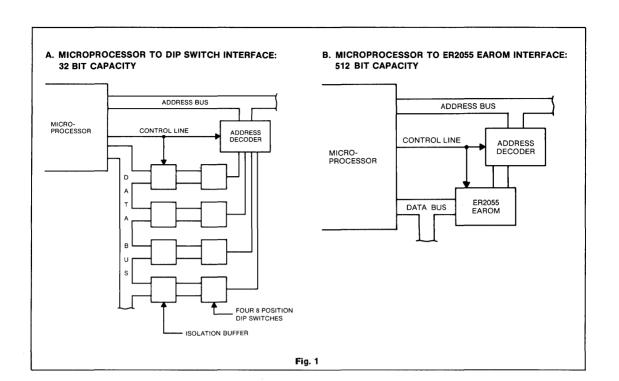

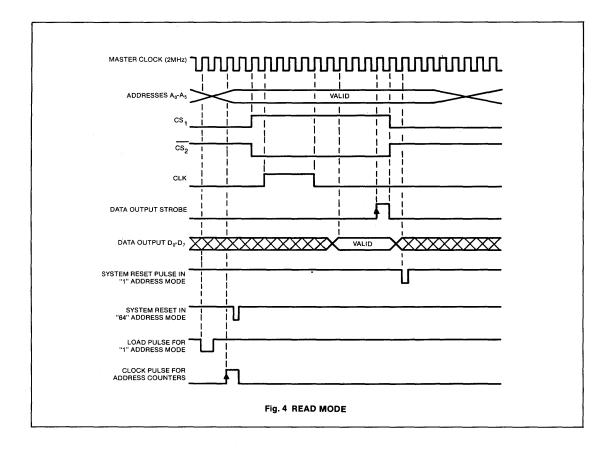

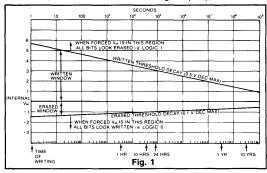

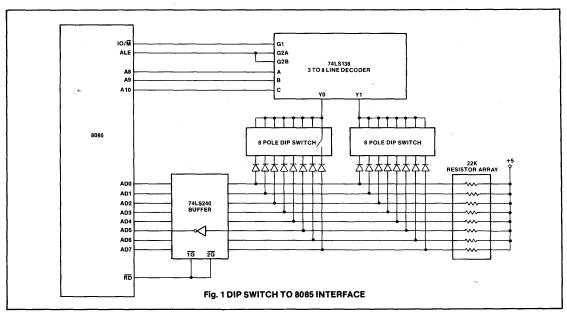

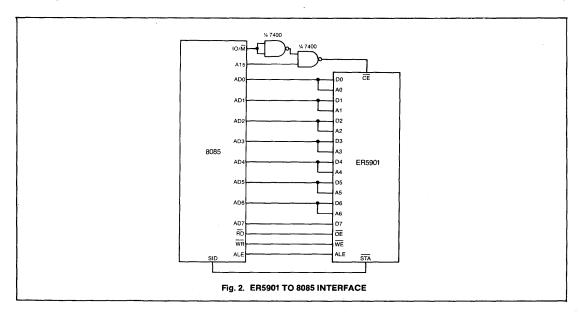

- 3. PROGRAM with separate address and data lines.